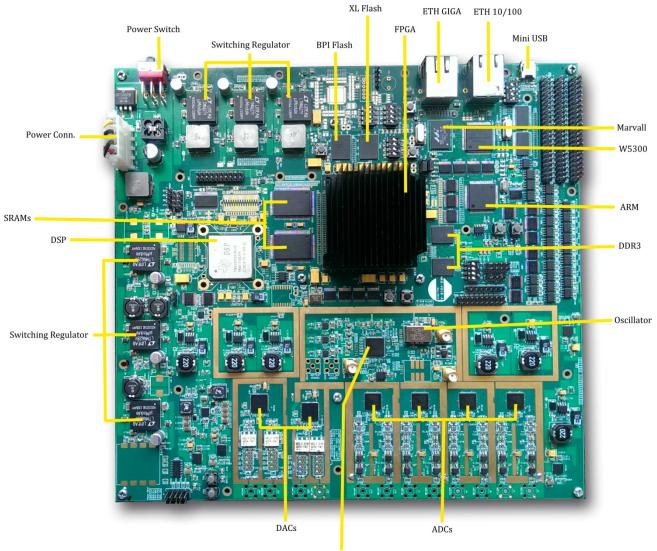

# NKS-V016-A Stand-Alone Board Virtex-6 & DSP High Performance Processing Platform 8- Channel 16-bit ADC 125MSPS 4- Channel 16-bit DAC 1GSPS

### Description

The NKS-V016-A processing board is a high performance industrial single card dedicated to high performance data acquisition and communications based on the Xilinx Virtex-6 LX365T FPGA family. The NKS-V016-A board enables designers to prototype high-performance digital transceivers. The board includes a DSP Processor (TMS320C6678) which incorporating the new and innovative C66x DSP core, this device can run at a core speed of up to 1.25 GHz. Additionally four D/A channels 16 bit resolution at maximum rate of 1GSPS per channel and eight A/D channels 16 bit resolution at maximum rate of 125 MSPS per channel are available. The sample clock can be supplied from PLL clock distributer, externally through a coax connection or supplied by an internal clock source.

### Application

- RADAR/SONAR

- Communications

- Diversity radio systems

- Multimode digital receivers (3G)

- GSM, EDGE, W-CDMA, LTE

- General-purpose software radios

- Broadband data applications

- I/Q demodulation systems

- Fire Control and Defense Systems

- Smart antenna systems

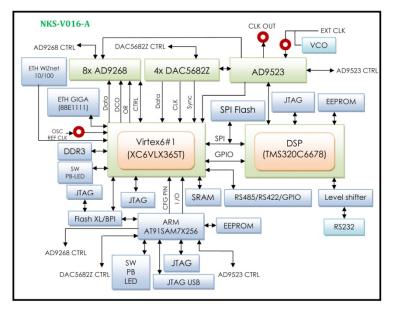

### **Functional Block Diagram**

#### WWW.NIKSOO.COM/NKS-V016-A

Support: support@niksoo.com Email: info@niksoo.com

# NKS-V016-A

## **Features**

### ADC's:

- 8 Channels, 16 bit, 125MSPS

- Differential Analog Input with 650MHz Bandwidth

- Analog Input Filter Options

- SNR = 75 dBFS @ 20 MHz and 125 MSPS

- SFDR > 80 dBc @ 20 MHz and 125 MSPS

- ENOB = 12.4 Bits @ 20 MHz and 125 MSPS

- Xtalk Isolation > 95dB

- Low Power: 750 mW @ 125 MSPS

- High Performance AC-Coupled Analog Input With 8 Channel AC/DC Coupled Switching Capability

- 1.8 V Analog Supply Operation

- 1.8 V CMOS or LVDS Output Supply

- Flexible Analog Input Range: 1V p-p to 2V p-p

- Pin Compatible with AD9258, AD9251, AD9231 and AD9204

### DAC's:

- 4 Channels, 16-Bit, 1GSPS Update Rate

- Analog Output with 500MHz Bandwidth

- Analog Output Filter Options

- Phase Noise > 100dBc @ 1kHz and 1GSPS

- Interleaved I/Q data for Dual-DAC Mode

- 2x-32x Clock Multiplying PLL/VCO

- 2x or 4x Interpolation Filters

- High Performance AC-Coupled Analog Output with 2 Channel AC/DC Coupled Switching Capability

- Pin Compatible with DAC5681

Other's:

- Virtex XC6VLX365T-3FFG1759C Xilinx Device

- Digital Signal Processing (DSP) TMS320C6678 TI Device

- ARM Microcontroller AT91SAM7X256 Atmel Device

- 4 Gb DDR3 Component Memory (Two [256 Mb x 8] Devices)

- 144 Mb @ 167MHz SRAM Component Memory (Two [4Mb x 18] Devices)

- Flexible PLL Clock Tree Enables (Internal Clock, External Clock, Internal Clock with External Reference)

- Ethernet PHY 10/100/1000 Interface with RJ-45 Connector for FPGA

- Ethernet WIZnet 10/100 Interface with RJ-45 Connector for FPGA

- Multi-boot Configuration

- 20x RS422, 5x RS485, 24x GPIO and 1x CAN BUS Serial Interfaces

- Status and Debug LEDs

- Power on/off Slide Switch

- Physical Dimensions (L: 249.9 mm, W: 233.2 mm)

- Operating temperature: 0°C to +85°C (Industrial)

- 12V External Voltage Supply

- Operation System Support: Windows & Linux

**Board Features**

Clock Distributor

## **Order Information**

|                                          | <u>NKS</u> - <u>V</u> | <u>/ 0</u><br> | 16 | <u>5</u> - <u>A</u><br> | 1 |

|------------------------------------------|-----------------------|----------------|----|-------------------------|---|

| Niksoo Mark ———                          |                       |                |    |                         |   |

| FPGA Family<br>V = Virtex<br>S = Spartan |                       |                |    |                         |   |

| Number of FPGA                           |                       |                |    |                         |   |

| FPGA Series                              |                       |                |    |                         |   |

| Revision Code                            |                       |                |    |                         |   |